Cryogenic Computing

Cryogenic Computing

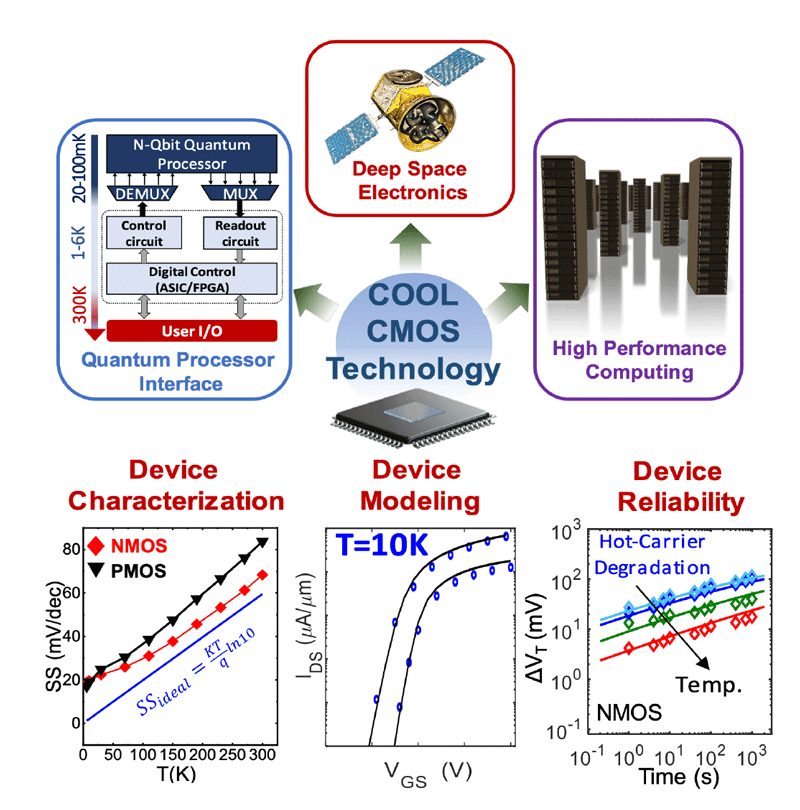

The improvement of CMOS performance (electrostatics, transport, parasitic resistance, reliability and self heating) at low temperature has raised interest in Cool-CMOS technology for a range of applications from high performance computing in data centers, to sensor interface circuits in space-crafts to Q-bit controller and read-out circuits in quantum processors. Imperative to understand the temperature dependent physics of electrostatics and transport in nanoscale MOSFETs as well as major device reliability mechanisms such as channel hot-carrier degradation and bias temperature instability. In this direction, the main research focus is to perform device characterization at low temperature, develop compact models for accurate prediction and optimization of system performance and reliability with Cool-CMOS.

Papers:

- Chakraborty, W. et. al. “Experimental Investigation of Sub-threshold Swing Degradation in HKMG MOSFETs at Cryogenic Temperature for Quantum Computing Application”, 77th Device Research Conference (DRC), 2019

- Chakraborty, W. et. al. “An Empirically Validated Virtual Source FET Model for Deeply Scaled Cool CMOS”, accepted in IEDM 2019

Funded by:

DARPA (DSSP Program)