Monolithic 3D Integration

Monolithic 3D Integration

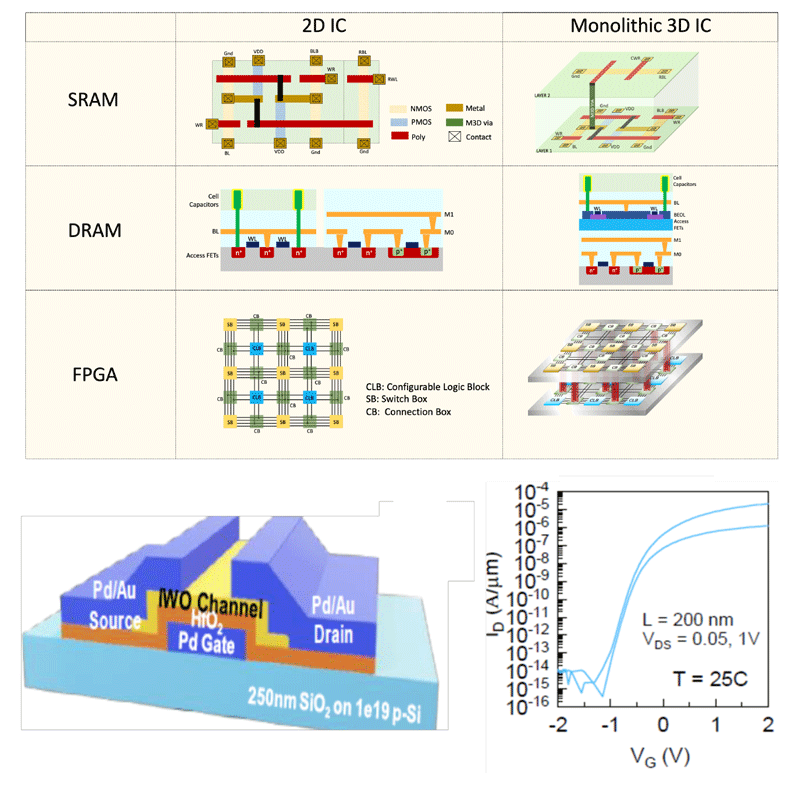

The manufacturers of high-performance logic are ardent champions of Moore’s Law, which has resulted in exponential increase in aerial transistor density to 100 million transistors per square millimeter of silicon real estate. Still, it is the memory chip makers who have already embraced the vertical or the third dimension to increase memory array density. To enable monolithic three-dimensional (M3D) integration of high-performance logic, one needs to solve the fundamental challenge of low temperature (<400C) in situ synthesis of high mobility n-type and p-type semiconductor thin films for fabrication of back-end-of-line (BEOL) compatible CMOS transistors under the constraint of limited thermal budget. We investigate various avenues towards achieving M3D ranging from selection and optimization of semiconductor materials to fabricating BEOL compatible metal oxide channel transistors. We are exploring a variety of applications from M3D SRAM to M3D DRAM to M3D FPGA.

Papers:

S. Datta et. al. "Back-End-of-Line Compatible Transistors for Monolithic 3-D Integration," in IEEE Micro, vol. 39, no. 6, pp. 8-15, 1 Nov.-Dec. 2019

Funded by:

GRC Global Research Corporation (Double check should this be Collaboration?)