High Performance CMOS

Negative Capacitance

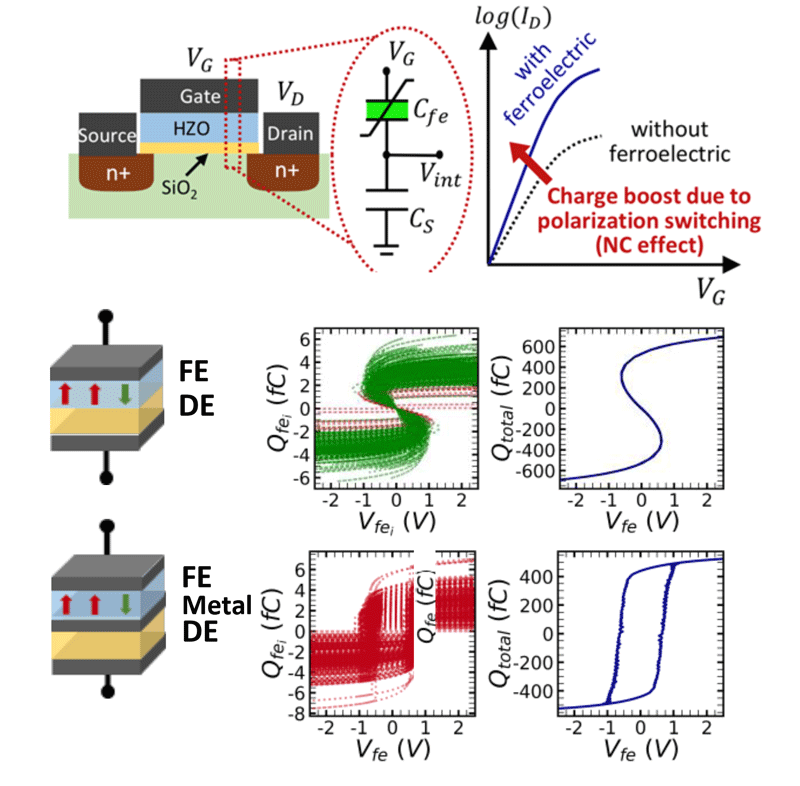

The phenomenon of negative capacitance (NC) in the ferroelectric-dielectric (FE-DE) based gate stack can provide a novel pathway to achieving sub-60 mV/dec sub-threshold swing in Ferroelectric FETs, and therefore improving the energy-latency product of transistors. Experimentally and theoretically, we are exploring multi domain switching dynamics that highlight the possibility of stabilizing negative capacitance without hysteresis and enable ferroelectric field-effect transistor from internal voltage amplification and associated channel charge boost.

Papers:

- Gomez, J., Dutta, S., Ni, K., Smith, J., Grisafe, B., Khan, A. and Datta, S., “Hysteresis-free negative capacitance in the multi- domain scenario for logic applications”, IEEE International Electron Devices Meeting (IEDM), 2019.

- Gomez, J., Dutta, S., Ni, K., Grisafe, B., Smith, J., Khan, A. and Datta, S., “Significance of Multi and Few Domain Ferroelectric Switching Dynamics for Steep-Slope Non-Hysteretic Ferroelectric Field Effect Transistor”, 77th Device Research Conference (DRC), 2019.

- Gomez, J., Dutta, S., Ni, K., Joshi, S. and Datta, S., “Steep Slope Ferroelectric Field Effect Transistor”, Electron Devices Technology and Manufacturing Conference (EDTM), 2019.

Funded by: